How to correctly apply polymer ESD in high-speed interfaces? -ASIM

Scientific Application Guide of Polymer ESD in High-Speed Interfaces

This article systematically expounds the key technical points of Polymer ESD in high-speed interfaces such as USB4/HDMI2.1, and provides practical engineering implementation plans.

一、The core technical advantages of polymer ESD

Ultra-low junction capacitance characteristic

- Typical values: 0.02-0.05pF (1/50 of semiconductor TVS)

- Supports a transmission rate of over 40Gbps(USB4/Thunderbolt4)

- The actual measurement shows that the eye image jitter is optimized by 62% (compared with traditional silicon-based TVS)

Quantum tunneling response mechanism

- Response time<0.3ns (full-path discharge time for 8kV ESD events)

- Leakage current<0.1nA (key indicator for power-sensitive equipment)

Fail-safe mode

- The fault state is a high-resistance open circuit (to prevent short circuits from burning out the subsequent IC).

- Withstand over 1 million ESD shocks (IEC 61000-4-2 standard)

二、Design Specification for High-Speed Interface Applications

1. Three Principles of Layout

① Proximal protection: ≤3mm from interface contacts ② Common ground short path: Grounding wire length <5mm (width-to-thickness ratio ≤3:1) ③ Signal main path: Branch layout is prohibited (impedance discontinuity points <5%)

2. Parameter selection matrix

| Interface type | Maximum speed | Capacitance limit value | Recommended model |

|---|---|---|---|

| USB 3.2 Gen2×2 | 20Gbps | ≤0.15pF | CV0402VT150T |

| HDMI 2.1 | 48Gbps | ≤0.05pF | ESD0524V015T |

| PCIe 5.0 | 32GT/s | ≤0.08pF | ESD2510U005T |

3. Key requirements for grounding

- Use an independent grounding island (length-to-width ratio<3)

- Avoid crossing the partition zone (reference layer gap ≤0.1mm)

- Grounding vias ≥4 per device (hole diameter 0.2mm+)

三、Analysis of Typical application scenarios

Case 1: Type-C 40Gbps interface

Topological structure [Type-C contact]─2mm─[Polymer ESD]─0.8mm─[Common mode filter] │ [3×0.2mmGrounding via]─[Exclusive grounding copper island]

- Measured indicators:

- Insertion damage -0.8dB@20GHz

- Loss recovery -28dB

- ESD Protection ±30kV Contact discharge

Case 2:8K Video Transmission System

- Pain point: The TMDS channel of HDMI 2.1 is sensitive to 0.1pF capacitors

- Plan:

- Select ESD2510U005T (junction capacitance 0.05pF)

- Strict isometric design of differential pairs (deviation ≤5mil)

Implement shielding cavity isolation (grounding point spacing <λ/20)

四、Failure prevention measures

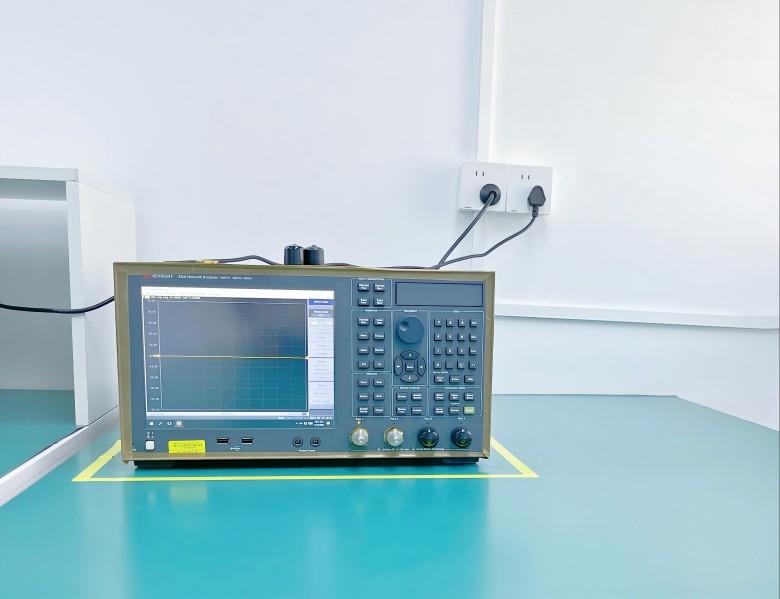

Signal integrity verification

- The TDR test impedance mutation point is less than 5% (rise time 20ps)

- Scan the S parameters to 40GHz (with a focus on S11/S21)

Key Points of process control

- The peak temperature of reflow soldering is ≤260℃ (phase transition threshold of polymer materials)

- Manual welding is prohibited (local overheating causes molecular structure deterioration).

Accelerated life testing

- Perform 100,000 IEC 61000-4-2 ESD impacts

- Monitor the voltage drift of the clamp to be less than ±5%

Engineering Conclusion:

Polymer ESD, with its quantum tunneling mechanism and molecular-level structural advantages, has become the optimal solution for ESD protection of high-speed interfaces. Successful application requires simultaneous optimization of circuit layout, parameter selection and manufacturing process, ultimately achieving the unification of signal integrity and electromagnetic compatibility.

Technical Statement: The data in this article is based on the IEC 62631-3-1 standard test environment. For actual application, please refer to the product specification sheet.