- Industry solution

Consumer electronics

Automotive electronics

Household appliances

Security monitoring

Industrial control

AI Intelligence

Medical and health care

Communication equipment

EMC design for USB2.0 port

EMC design of USB Type-C port

EMC design of HDMI port

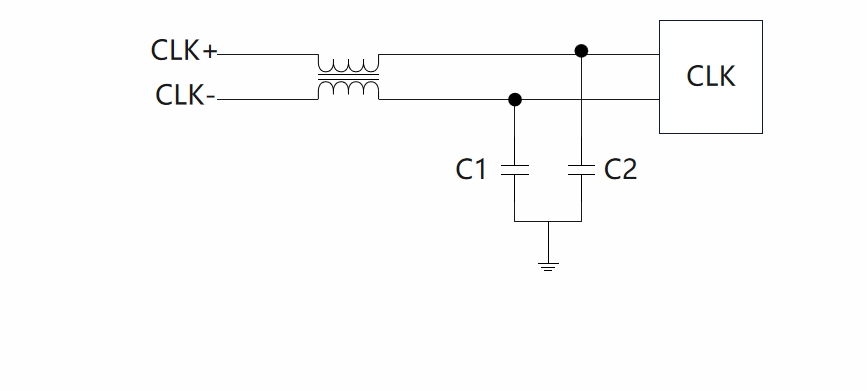

RJ45/ 100M network port design

EMC design of TF card port

EMC design of DC power supply port

EMC design of AUX port

EMC design of VGA port

EMC design for USB3.0 port

RJ45 100M network port (with POE) design

RJ45 Gigabit network port design

RJ45 Gigabit network port (with POE) design

Search

Popular Search Terms:

-

-

- EMC design for USB2.0 port

- EMC design of USB Type-C port

- EMC design of HDMI port

- RJ45/ 100M network port design

- EMC design of TF card port

- EMC design of DC power supply port

- EMC design of AUX port

- EMC design of VGA port

- EMC design for USB3.0 port

- RJ45 100M network port (with POE) design

- RJ45 Gigabit network port design

- RJ45 Gigabit network port (with POE) design

-

-

-

-

Service

Do you need further assistance?

Please tell us your specific research needs and we will reply to you as soon as possible.

![]()

Code*